Samsung Foundry Announces 10nm SoC In Mass-Production

by Andrei Frumusanu on October 17, 2016 5:40 AM EST- Posted in

- Semiconductors

- Samsung

- fabrication

- 10LPE

Today Samsung announced mass production of a SoC built on its third-generation 10nm "10LPE" manufacturing node. It was only this January that Samsung announced mass production of its 14LPP process that ended up being used in the Exynos 8890 and the Snapdragon 820 powering up a large amount of flagship devices this year.

This time around the announcement comes quite early compared to the past 2 years and I wasn't expecting any news from the foundry till maybe later in the quarter. This does however bode well for the SoCs built on the process as they seem they'll be able to easily make the spring 2017 device release schedule.

There wasn't any specification as to what kind of SoC the mass production announcement is refering to, but it's very likely we're talking about S.LSI's next generation Exynos - or maybe even Qualcomm's Snapdragon 820 successor, both of which we'll hopefully hear official announcements from in the coming months.

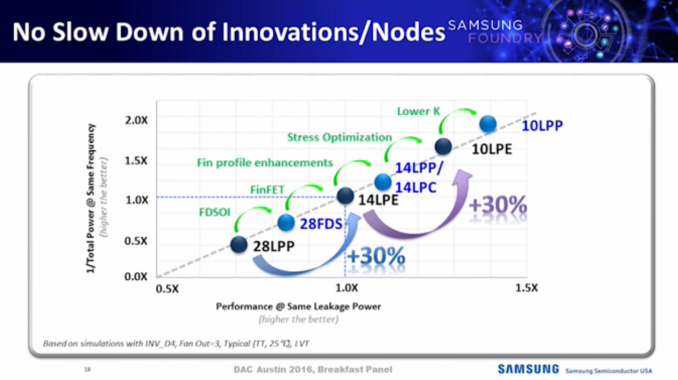

Samsung’s new 10nm FinFET process (10LPE) adopts an advanced 3D transistor structure with additional enhancements in both process technology and design enablement compared to its 14nm predecessor, allowing up to 30-percent increase in area efficiency with 27-percent higher performance or 40-percent lower power consumption. In order to overcome scaling limitations, cutting edge techniques such as triple-patterning to allow bi-directional routing are also used to retain design and routing flexibility from prior nodes.

Credit: DAC 2016 Samsung/Synopsys Breakfast - Ready to Design at 10nm!

The process promises some significant speed and power efficiency advantages over current generation designs so it's likely the next generation of devices will see a large boost, similarly to how the first 14/16 SoCs had large improvements over previous generation 20/28nm designs.

Interestingly the new SoCs will have an edge on recent and upcoming designs still being released on 16nm manufacturing processes, such as Apple's A10 or other TSMC customers who have to wait till next year for 10FF. This presents itself as an opportunity for vendors such as Samsung and Qualcomm to try to close the performance and efficiency gap seen in the current generation through the manufacturing process' good timing.

Source: Press Release

92 Comments

View All Comments

witeken - Tuesday, October 18, 2016 - link

Ehh, Samsung's "10nm" node will be only a meager 1.2x denser than Intel's 14nm (in terms of SRAM density) which launched 2 years ago ;).Intel 14nm: 0.0588um2 (regular SRAM)

Samsung 10nm: 0.049um2 (regular SRAM)

(There's also high density SRAM, which is 1.6x denser for Samsung, but high density SRAM is in fact not used and just sucks in terms of performance.)

psychobriggsy - Tuesday, October 18, 2016 - link

IIRC Intel's 22nm was Tri-Gate (three fins) at 22nm, meaning that their 22nm transistors were nearly as large as a 28nm planar transistor in practice.I think they went down to 2 fins at 14nm however.

Note that their latest 14+ for Kaby Lake is lower density than their previous 14nm, so they could increase clocks a bit. Whether that means they're tri-gate again, or just longer/wider dual-gate I don't know.

witeken - Tuesday, October 18, 2016 - link

You are misunderstanding Tri-Gate / finFET. Those two names refer to the transistor architecture: it's a 3D transistor that has 3 gates. The number of fins per transistor is entirely up to the SoC designer and can be chosen freely per transistor. Increasing the number of fins increases the drive current (performance). At 14nm, Intel has lowered the variability of their transistors, so they had to use fewer fins per transistor, which gave them an undisclosed density boost.The name of the node (22nm, 28nm, etc.) is just a marketing name that does not meaning anything. If you want to compare some characteristic of a node, for instance density, there a specific features or characteristics or feature sizes that you have to compare. A process node is so much more nuanced than a single marketing name. It doesn't does billions to develop a new node for nothing...

DanNeely - Monday, October 17, 2016 - link

In terms of actual feature size, or just branding? I know Intel's 14nm process had significantly smaller features than Samsung's 14 and a larger edge than 14 vs 16 would imply vs GloFo's.Toss3 - Monday, October 17, 2016 - link

Isn't 10nm FF the same size as the regular 14nm node, as in Intel's 14nm == Samsung's 10nm FF? I remember reading something about how both TSMC's 16nm FF and Global Foundries' 14nm FF were basically just modified 20nm nodes, marketed as being smaller than they actually are.lefty2 - Monday, October 17, 2016 - link

No. Samsung's 10nm is actaully 10% denser than Intel's 14nm. You can see how the different nodes stack up here: https://www.semiwiki.com/forum/content/6160-2016-l...And another thing Intel can call it's node anything it wants to. It simply made a poor choice calling it 14nm from a marketing point of view.

Toss3 - Monday, October 17, 2016 - link

Yeah, but look at Intel's 10nm - 9.5nm, while Samsung's is 12nm (shouldn't it be called 12nm?). Didn't mean that they are exactly the same, but that only a part of samsung's 10nm is actually 10nm. Intel's nodes are, as far as I understand it, "real nodes"; as in actually as small as the name would suggest. Probably a lot more to it than that, and I'd love to learn more about it. Maybe anandtech should do a deep dive into the different nodes?lefty2 - Monday, October 17, 2016 - link

You don't get it. The node name is a made up label. It's only loosely related to the density. There is nothing in a 10nm node that measures 10nm.Also, you seem think Intel is automatically superior to everyone else simply because they have higher density. Intel suffer poor yields because of the aggressive tolerances they use. That's why Intel have to start with small cores on a new node. The yields are too low to manufacture the larger die CPUs.

fanofanand - Monday, October 17, 2016 - link

This isn't entirely accurate, the node label is supposed to reflect at least one feature size correlating to the node label. So a 14nm node should have at least one feature that is at 14nm. It certainly doesn't mean that all features are at that size, but at least one should be. Anandtech actually wrote about this a few years back, so hopefully my memory is serving me correctly.lefty2 - Monday, October 17, 2016 - link

What I said is correct. On Intel's 14nm node the gate pitch has been measured at ~70nm and fin pitch at ~42nm and that is what defines the density. http://www.extremetech.com/computing/193200-intels...There is nothing that measures 14nm. But you are welcome to provide a link to any article that proves there is.