Intel And Micron Launch First QLC NAND: Micron 5210 ION Enterprise SATA SSD

by Billy Tallis on May 21, 2018 4:30 PM EST

Intel and Micron are announcing today that their jointly-developed QLC NAND flash memory is now available, and Micron is now shipping the first solid state drive based on QLC NAND: an enterprise SATA drive branded the 5210 ION series. This will join the TLC-based 5200 family as a lower-cost tier with reduced write performance and endurance.

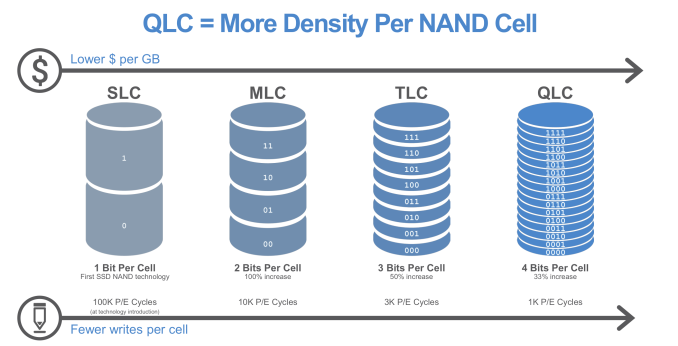

QLC NAND flash memory stores four bits of data per memory cell, providing a 33% capacity boost over three bit per cell TLC NAND, which is now used in almost all SSDs. The downsides are that QLC NAND has lower write endurance on the order of 1000 program/erase cycles, and lower write performance. Both of these are consequences of the difficulty of discriminating between 16 possible voltage levels within a memory cell, as compared to the 8 voltage levels required to store three bits per cell.

The cost reduction brought by QLC NAND is a much-awaited advance for enterprise storage. Most NAND flash manufacturers have started sampling QLC NAND within the past year, generally built on the same 64-layer 3D NAND processes that current-generation TLC NAND uses. Micron has previously shown wafers of 512Gb 64-layer QLC when announcing the addition of QLC to their roadmap, but today they are also announcing a 1Tb 64L QLC part—the first 1Tb memory chip to hit commercial availability. That 1Tb part is organized as four planes that can be processing I/O commands in parallel, compared to two planes for previous Intel/Micron NAND parts. This helps offset most of the performance loss associated with increasing per-die capacity. Thanks to the "CMOS under the array" design of Intel/Micron 3D NAND, the extra peripheral circuitry requried by doubling the number of planes doesn't add much to the overall die size.

It was initially feared that QLC write endurance would be low enough that drives would need to be treated more or less as write-once, read-many (WORM) devices, requiring careful handling on the software side. With multiple manufacturers now rating their QLC NAND for around 1k P/E cycles, it is clear that QLC-based SSDs aren't too fragile and can handle many existing workloads without needing major software changes to reduce writes.

Micron is primarily marketing the 5210 ION SSDs as replacement for hard drives, rather than replacements for any existing tier of enterprise SSD products. In this role, the 5210 ION will have clear advantages in density (with 2-8TB per 2.5" drive) and performance. QLC NAND only provides incremental improvements to cost, so the 5210 ION won't be matching 7200RPM hard drives for price per GB, but 10k RPM drives will probably be feeling the pressure, especially from TCO calculations that take into account the power efficiency advantages of SSDs.

Micron isn't providing detailed specifications for the 5210 ION series at this time, but we can read between the lines. The 5210 ION series is based on the same controller and firmware platform used for the 5200 and 5100 families. That means a Marvell 88SS1074 controller, and Micron-written firmware with features like their FlexCapacity configurable overprovisioning to trade capacity for performance and endurance.

| Write Endurance (Drive Writes Per Day) |

|||||

| Capacity | 5210 | 5200 | |||

| ION | ECO | PRO | MAX | ||

| 240 GB | 5.0 | ||||

| 480 GB | 1.0 | 5.0 | |||

| 960 GB | 1.0 | 1.3 | 5.0 | ||

| 1920 GB | <1 | 1.0 | 1.7 | 5.0 | |

| 3840 GB | <1 | 1.1 | 2.5 | ||

| 7680 GB | <1 | 0.6 | |||

Specific performance numbers haven't been disclosed, but Micron has indicated that both random and sequential read performance will be comparable to the 5200 family—meaning the 5210 can saturate the SATA link at higher queue depths. Write performance will be lower than the 5200 ECO but still higher than what a hard drive can deliver, especially for random writes.

The most important question is what the write endurance of the new QLC-based SSDs will be. The 5210 ION's endurance rating will be less than that of the 5200 ECO, which is rated for around 1 DWPD in most capacities. Micron indicates that their QLC NAND is good for around 1k Program/Erase cycles, which suggests a limit of at most about 0.5 DWPD before write amplification is taken into account. This is still higher than many consumer SSDs, where 0.3 DWPD is a typical rating for entry-level SATA SSDs with 3D TLC NAND.

When used for tasks where the performance of hard drives is currently adequate, the write endurance of the 5210 ION shouldn't be much of a problem. An endurance rating of about 0.1 DWPD would be sufficient for the 5210 ION to handle more random writes over its 5-year warranty than a hard drive can provide, but for sequential workloads it will still be possible to wear out the 5210 by writing to it at hard drive speeds. But Micron isn't recommending the 5210 ION for continuous video recording; instead they are pitching it for workloads that are at least 90% reads.

The Micron 5210 ION is now shipping to select customers with capacities from 1.92TB to 7.68TB, and will be broadly available this fall. Exact pricing and specifications will be released at that time. Intel has not yet announced any products using QLC NAND, but we expect product announcements and possibly shipments in time for Flash Memory Summit in August.

Intel and Micron are also working on their next generation 3D NAND manufacturing process, which increases the layer count to 96. This will provide a bigger density boost than a switch from TLC to QLC. It appears that development is currently focused on 96L TLC parts of unspecified capacity, but they will surely be followed by 96L QLC parts as well. Beyond 96 layers, Intel and Micron's long-standing partnership in flash memory technology will come to an end, with the two companies developing their flash independently. Neither company has shared any roadmap information going past this split, so it is not clear to what extent their designs will diverge with what will probably be the 128-layer generation.

Source: Micron

38 Comments

View All Comments

jjj - Monday, May 21, 2018 - link

Micron did provide some details on the NAND gen beyond 96 layers in their financial event today. Had the audio in the background but could not fully focus on it so might have missed a few bits, or more than a few.Anyway, the few bits I do remember.

Developing a "novel charge trap"

96 layers NAND will use string stacking, 48+48

96 layers provides over 30% in bandwidth and over 40% lower power

XPoint gen 2 moved from R&D to production.

XPoint products in the later part of 2019 - no idea if fiscal or calendar but assuming calendar.

And there was a slide where cost reduction for gen 2 seemed minimal so would assume 4 layers and no horizontal scaling but that's based on too little so could be wrong.

Billy Tallis - Monday, May 21, 2018 - link

Good to know. It did seem like the most likely reason for ending the partnership was that one of them wanted to switch from 3D floating gate to charge trap, and Micron seems to be the more likely one to want to make that jump.jjj - Monday, May 21, 2018 - link

I don't agree, think it's more likely that Intel wanted to use existing clean room capacity instead of the JV and they are also likely to sell their NAND operations in a few years.And Micron likely wasn't eager to renew the supply agreements they had with Intel and I think those expire one this year and one in 2019.

China is likely to ramp NAND beyond 2020, seems likely at this point so Intel would be better off selling to China or Micron. They likely needed their own technology to be able to sell to anyone but Micron and having their own prod , outside of the JV is way better too. So they create value right now with their own NAND nd production and then dump it for quite a few billions.

jjj - Monday, May 21, 2018 - link

They have also mentioned developing HBM, I think it's the first time they mention it.Using TSV in sever DRAM was mentioned.

And new nodes for DRAM beyond 1z, 1alpha and 1beta but not sure if those new nodes or packaging focus. No EUV for these new nodes either.

iwod - Tuesday, May 22, 2018 - link

TSV DRAM? Is that part of the DDR5 specification?jjj - Tuesday, May 22, 2018 - link

Safe to assume it's just a packaging solution used where/when it makes sense.jjj - Monday, May 21, 2018 - link

Correction here - 4th gen provides 30% more BW and 40% lower power vs 96L.And the first 96L die seems to be 512Gb.

iwod - Tuesday, May 22, 2018 - link

I don't mind about the current pricing of Xpoint. The problem is, it is not fast enough in latency and bandwidth as initially promised, endurance too. And it doesn't seem they are shipping in huge quantities.I am still waiting to see Quad Channel, 8 x 64GB Xpoint DIMM performance in Database. Assuming it kept with its 10x reduction per GB pricing. these should be a very good trade off. Giving up a 5-10ms in Database performance for 10x more capacity. ( Assuming your Apps is not latency critical )

jjj - Tuesday, May 22, 2018 - link

Gen 1 XPoint is likely to never be ramped to substantial volumes and it is running at a substantial loss. Gen 2 could even be just improvements for manufacturability with no vertical scaling and minimal or no horizontal scaling. Likely when they show small costs gains they compare at mature yield and then, the gains in practice will be much large once Gen 2 is ramped and gets to yield- does not mean we seem substantially lower prices in retail.The 10x lower cost vs DRAM might be misleading, likely an aspirational goal for a future gen with more layers.

Forgot to mention in my previous comments that Micron will be launching NVMe SSDs in the next few quarters.

ZeDestructor - Monday, May 21, 2018 - link

Any news on the price?