Hot Chips 2020 Live Blog: Intel's Tiger Lake Mobile CPU (12:30pm PT)

by Dr. Ian Cutress on August 17, 2020 3:30 PM EST- Posted in

- CPUs

- Intel

- Mobile

- Notebooks

- Live Blog

- 15W

- Tiger Lake

- Hot Chips 32

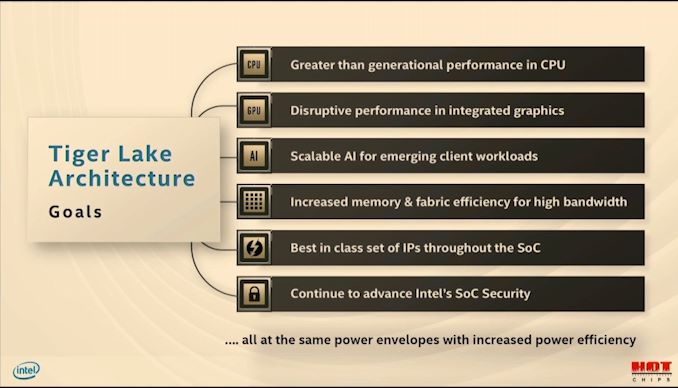

03:31PM EDT - Tiger Lake - generational improvement for graphics and CPU

03:31PM EDT - From 9W to 65W

03:32PM EDT - New AI features for new workloads

03:32PM EDT - USB4, PCIe4, TB4

03:32PM EDT - Increased power efficiency

03:33PM EDT - More cache, more performance, better efficiency, more headroom, more features

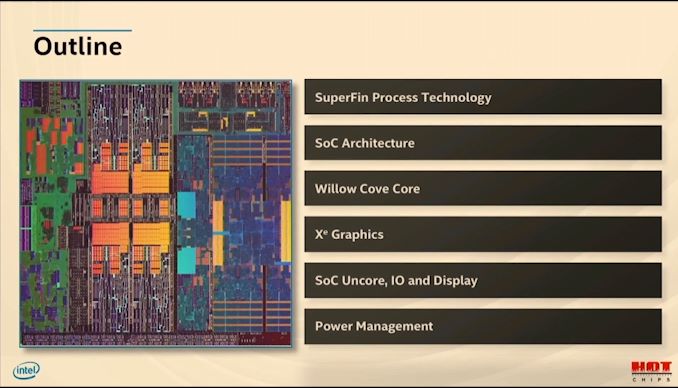

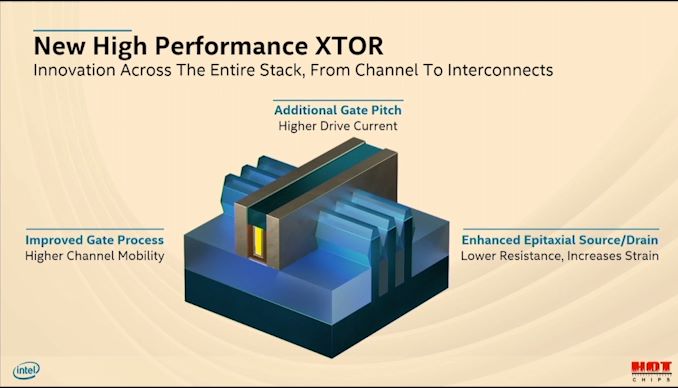

03:34PM EDT - New process technology

03:34PM EDT - new transistor

03:34PM EDT - SuperFin

03:35PM EDT - optimized non-perf critical IPs for the new transistor to allow for more headroom for the perf-critical stuff

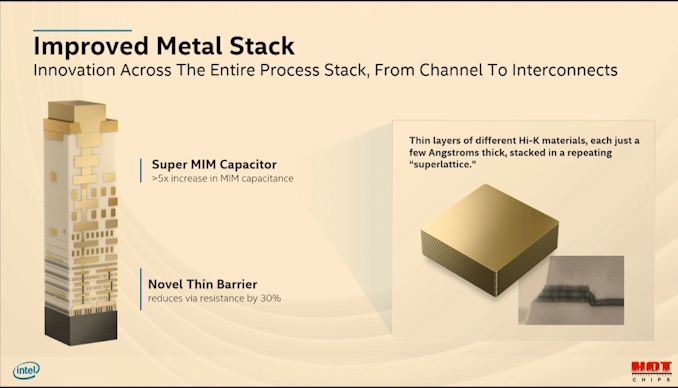

03:35PM EDT - Improved Metal Stack

03:35PM EDT - To new high perf layers at the top

03:36PM EDT - New SuperMIM

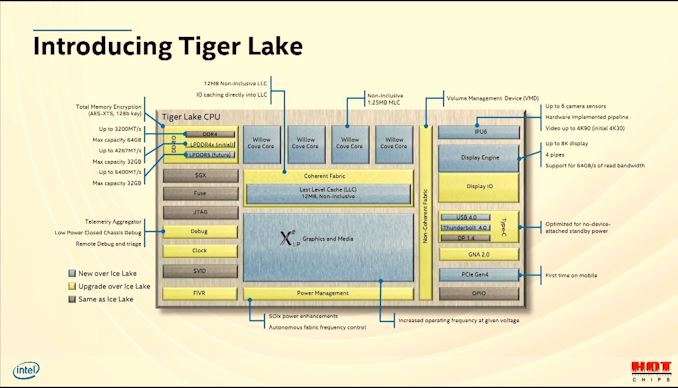

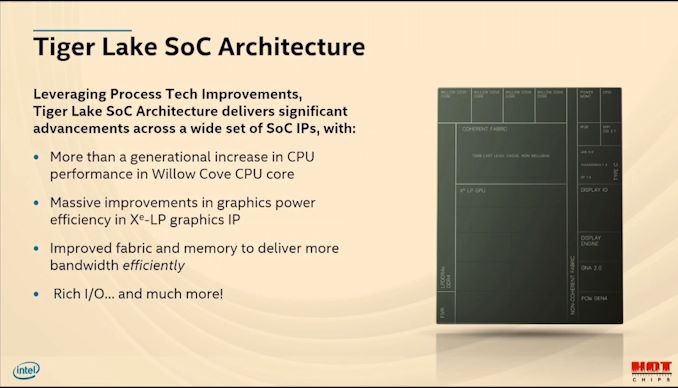

03:36PM EDT - Here's the high level diagram

03:36PM EDT - Different power envelopes might have different amount of cores

03:36PM EDT - (which means 8 core is coming later at 65 W)

03:37PM EDT - Four Willow cove cores, 96 EUs of Xe graphics

03:37PM EDT - LPDDR5-5400 support, PCIe 4.0 x4

03:37PM EDT - 12 MB non-inclusive L3

03:37PM EDT - 1.25 MB non-inclusive L2

03:37PM EDT - 4x4K display pipes

03:38PM EDT - IPU6 - two different flavors based on the chip config (?!?)

03:38PM EDT - Improved Debug

03:39PM EDT - GNA 2.0 does up to 38 GigaOPs, 1 GOP per watt (and it scales)

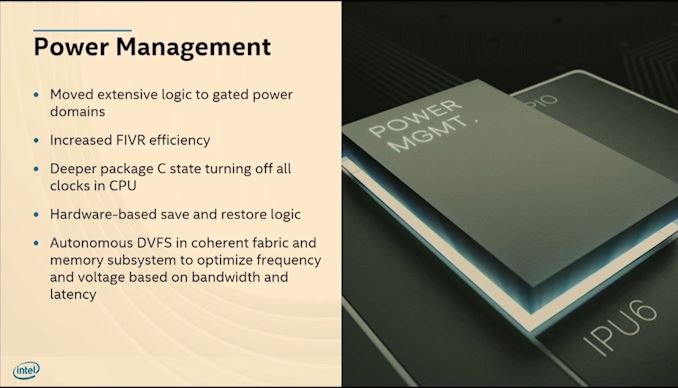

03:40PM EDT - Better FIVR

03:41PM EDT - Total Memory Encyption support

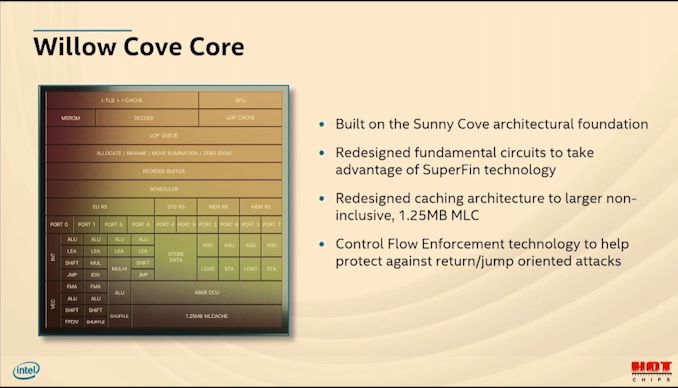

03:41PM EDT - Willow Cove in Tiger Lake

03:41PM EDT - Built on Sunny Cove base

03:42PM EDT - Had three options - IPC, improve circuits on freq for SuperFin, or a mix

03:42PM EDT - The second was used - focus on frequency

03:42PM EDT - Also cache adjustments and security

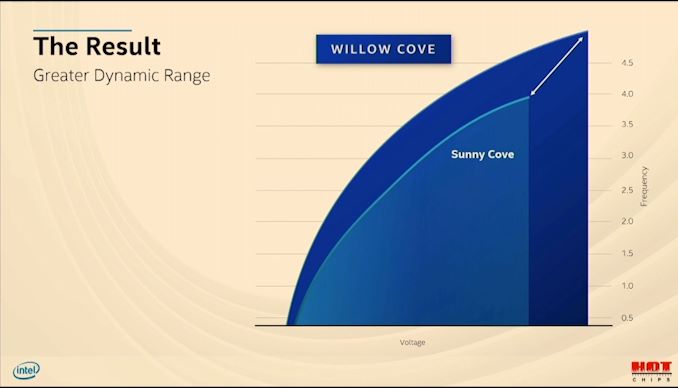

03:43PM EDT - Willow Cove has a better dynamic range - better perf/watt at all points and much higher voltage/freq

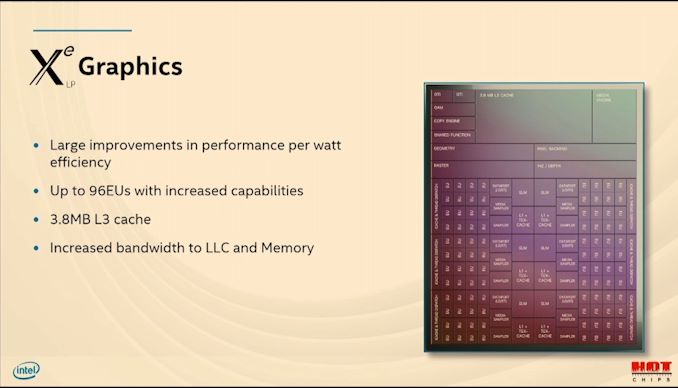

03:44PM EDT - Now to 96 EUs

03:44PM EDT - More info on Xe later

03:45PM EDT - Increased bandwidth

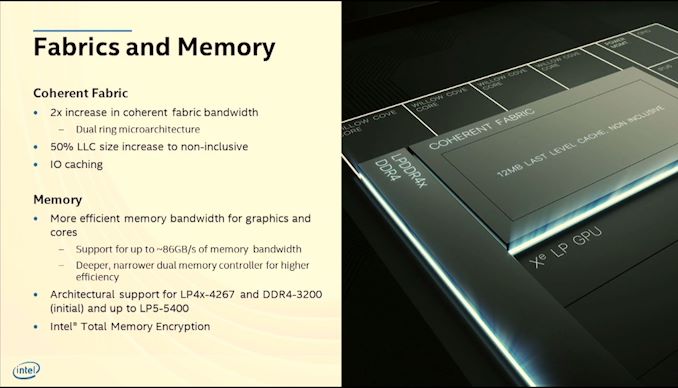

03:45PM EDT - Dual ring architecture

03:45PM EDT - IO caching

03:46PM EDT - Up to 86 GB/s on DRAM

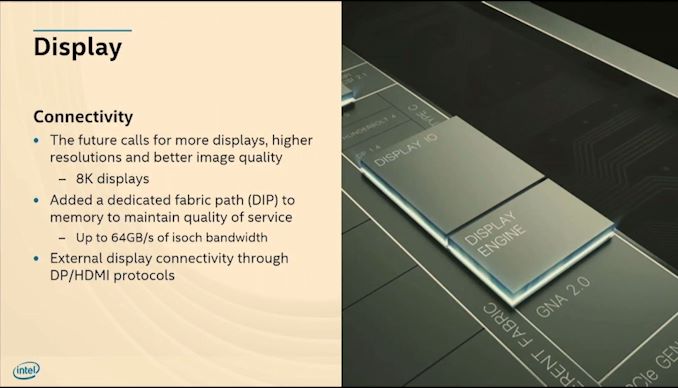

03:47PM EDT - Increased display support - but depends on memory configurations. Added dedicated fabric path to memory, up to 64 GB/s

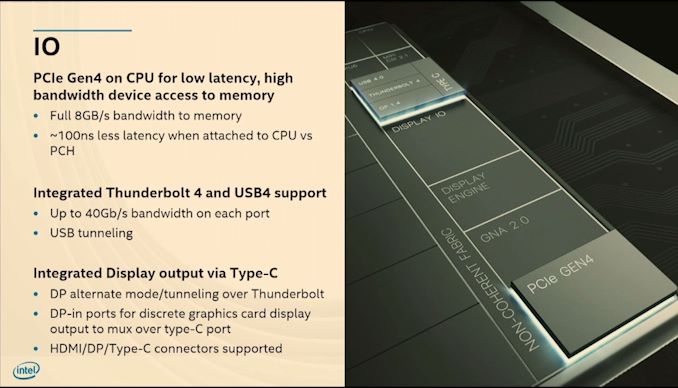

03:48PM EDT - PCIe 4.0 at 8 GB/s

03:48PM EDT - 100ns less latency for CPU attach compared to PCH attach

03:48PM EDT - Integrated TB4 and USB4, full compliance

03:48PM EDT - Display via Type-C using DP tunneling over TB

03:50PM EDT - Overall better power management for better idle power and quicker entry/exit

03:50PM EDT - DVFS on fabric

03:52PM EDT - More than a generational improvement in a single product cycle

03:53PM EDT - Q&A time

03:54PM EDT - Q: Only 4 CPU cores? What's the range? A: Will depend on the SKU config, announced in product launch in September.

03:54PM EDT - Q: Additional latency for TME? A: No disclosing.

03:54PM EDT - Q: Perf impact of TME? A: See the product launch at Sep 2

03:55PM EDT - Q: BW of TME? A: No loss of BW

03:55PM EDT - Q: PL2? A: See Sep 2 product launch.

03:56PM EDT - Q: Is incoming PCIe traffic cached in LLC? A:You can.

03:56PM EDT - Q: What sort of frequency is DVFS? A: No hard numbers. We sample the utilization and we can offer a fine granularity. (so once per hour?)

03:57PM EDT - Q: L2 latency with increased cache size? A: No answer.

03:58PM EDT - Client have always used L3 is inclusive - we now use non-inclusive. Once you grow that L2 cache to 1.25 MB, making L3 inclusive would consume 5 MB.

03:59PM EDT - Now there's an hour break for lunch, before Raja's keynote. Come back then!

41 Comments

View All Comments

yeeeeman - Monday, August 17, 2020 - link

AMD has the benefit of using tsmc process. Also 10w is doable at very low frequency with Renoir....4900h at high frequency is also very close to 65 eattsdotjaz - Tuesday, August 18, 2020 - link

10W Renoir would have too much performance and cost penalty, it wouldn't be economical especially when 7nm is in short supply.Technically it might be doable, but in reality it isn't. AMD wouldn't do it. Van Gogh with native 1CCX would be better suited for sub-15W SKUs.

Valantar - Tuesday, August 18, 2020 - link

Sure, if you let it run freely, but the frequency they're able to mintain at both 65 and 45 watts is much higher than competing Intel CPUs. AMD is able to keep boosting above bse even at 45W (and even at 35W for the better binned HD , which is out of the reach of any current Intel chip. Guess we'll see if the new 10nm process changes that.mikk - Monday, August 17, 2020 - link

Depends on the performance of these cores and don't forget this is probably PL2 because TGL-H should have 45W PL1.xenol - Monday, August 17, 2020 - link

Strange, I'm pretty sure one of the cellphone/tablet SoC makers can do 8 cores for less.IntelUser2000 - Monday, August 17, 2020 - link

Sure, but that's 4x Big + 4x Little.Drumsticks - Monday, August 17, 2020 - link

Just because they have a 10W 8 core doesn't imply that it doesn't go higher. See 4900H as others have said. Just because Intel is making a 65W 8 core doesn't mean they couldn't have made a smaller one if they chose to.Decisions to make 4 core mobiles aside, Tiger Lake seems compelling. If it has a meaningful ST performance increase then Renoir, has better perf/w, and better graphics, I'd give up the performance of an 8 core in my thin and light for everything that's gained there. That said, the MT performance of Renoir will still be unrivaled; we'll have *gasp* highly competitive products from both sides with distinct advantages. Somebody point out the last time THAT happened.

brantron - Monday, August 17, 2020 - link

For thin and light, most people would also be upgrading from a lower clocked Skylake / Kabylake dual-core, not a higher clocked Whiskeylake / Cometlake quad-core.My favorite thin and light is the XPS 13, and I doubt it will have an AMD anything, this year or next, so it's not much of a decision process.

However, if more Surface updates include AMD options, that would change things at the high end to apples vs. apples for a lot of people.

Farfolomew - Thursday, August 20, 2020 - link

Not necessarily, Kaby Lake Refresh came out in August 2017, three years ago now. By the time Tiger Lake comes out, that will be over three years that 4-core designs have been offered in the Laptops U-class chips. Many people and businesses looking to upgrade may already have 4-core chips and see that Tiger Lake is only 4 cores and Renoir is 8.Spunjji - Tuesday, August 18, 2020 - link

The fact that Intel are not making an 8-core CPU below 65W on 10nm really does suggest they can't - because otherwise they most definitely would, and have the ability to replace their whole 14nm range.