Spotted At Hot Chips: Quad Tile Intel Xe-HP GPU

by Ryan Smith on August 17, 2020 7:00 PM EST- Posted in

- GPUs

- Intel

- Xe-HP

- Hot Chips 32

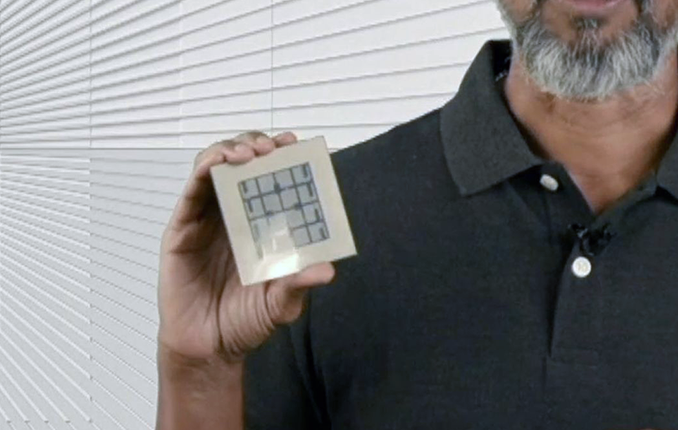

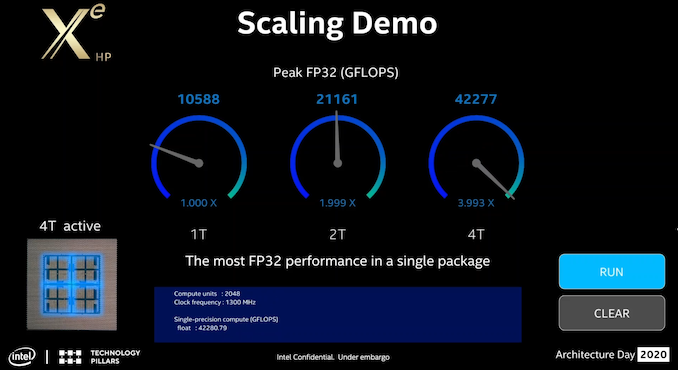

At last week’s Intel Architecture Day, Intel’s chief architect, Raja Koduri, briefly held up the smallest member of the company’s forthcoming Xe-HP series of server CPUs, the one tile configuration. Now, only a few days later, he has upped the ante by showing off the largest, four tile configuration.

Designed to be a scalable chip architecture, Xe-HP is set to be available with one, two, or four tiles. And while Intel has yet to disclose too much in the way of details on the architecture, based on their packaging disclosures it looks like the company is using their EMIB tech to wire up the GPU tiles, as well as the GPU’s on-package HBM memory.

Assuming it makes it to market, a multi-tiled GPU – essentially multiple GPUs in a single package – would be a major accomplishment for Intel. GPUs are notoriously bandwidth-hungry due to the need to shovel data around between cores, caches, and command frontends, which makes them non-trivial to split up in a chiplet/tiled fashion. Even if Intel can only use this kind of multi-tile scalability for compute workloads, that would have a significant impact on what kind of performance a single GPU package can attain, and how future servers might be built.

27 Comments

View All Comments

psychobriggsy - Wednesday, August 19, 2020 - link

I would presume that from the overall GPU viewpoint, there was no observable effect of the chiplets, due to the thousands of inter-chiplet I/Os keeping the device appearing to work as a single entity.Very different from SLI, which is two+ very separate entities with their own memory pools and independent operation, with some syncing and frame copying.

Kevin G - Monday, August 17, 2020 - link

This is what Intel needs to be doing on the CPU side of things. Throw their IO logic to a separate die and scale up the number of CPU cores via EMIB/interposers. You'd think that Intel's "mesh" topology would lend itself to such scaling.yeeeeman - Tuesday, August 18, 2020 - link

They will probably do it with Alder Lake since we don't know yet what the packing tech will be. From Intel slides I understand they will use the same kind of techniques like in Lakefield, so base die with IO and top die compute. Also, more cores is not the only solution....Intel can make their big cores fatter and add SMT4 or even SMT8 and boom, they have 64 threads from 16 cores CPUs. Sure, performance wise they won't be the same, but who cares, in desktop space basically no one uses more than 8/12/16 cores...yeeeeman - Tuesday, August 18, 2020 - link

Looks like. Also, 10Tflops of FP32 would make a very nice midrange GPU in 2021.TrevorH - Tuesday, August 18, 2020 - link

The main picture is presumably a block of 16 of them in one package. Or at least I hope it is or we'll need to go back to 1980's era luggable laptops to fit that in...tipoo - Tuesday, August 18, 2020 - link

These won't be for laptopsneojack - Tuesday, August 18, 2020 - link

those are for huge expension cards, probably watercooled