Intel Unveils the Xeon Scalable Processor Family: Skylake-SP in Bronze, Silver, Gold and Platinum

by Ian Cutress on May 4, 2017 8:00 AM EST

One of the more interesting elements of last week’s news was that some of the names of the future Intel Xeon processors, based on the Skylake microarchitecture, were accidentally ‘leaked’ via an official Intel Product Change Notification. In that list, we learned that the processors will have a new naming scheme, and we saw Gold and Platinum processors based on the LGA3647 socket having a wide range of numbers, but no core counts or clock speeds.

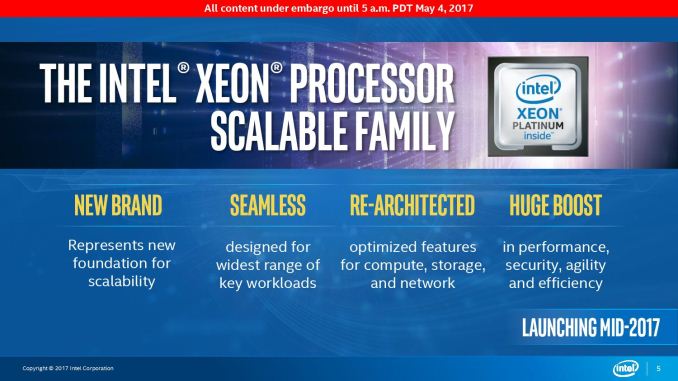

Today’s unveiling is minor, but an official approach to the new platform. Due to the way that Intel is expanding its reach from processors to networking to FPGAs and beyond, it has been decided that a new naming scheme needs to be in place. Thus the Xeon E/EP/EX naming regime is being reintegrated into what is now called the ‘Xeon Scalable Processor Family’, of which the first set of products will be based on the Skylake microarchitecture. This is where the ‘SP’ in ‘Skylake-SP’ comes from, as the other abbreviations are now retired.

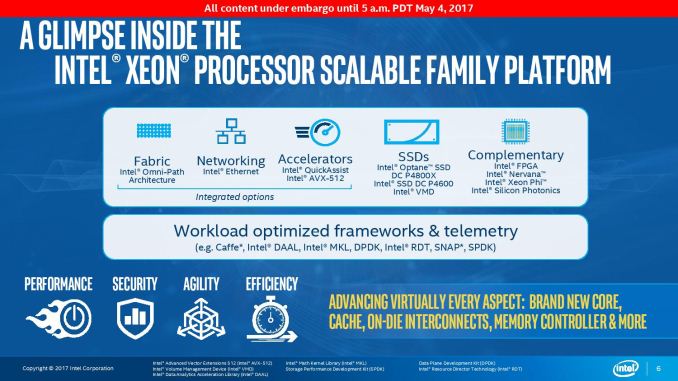

The core of Intel’s unveiling today revolves around the different processor levels they will be offering, and where the new integrated options will fit in the new stack. In the slide above, Intel lists three integrated options: Omni-Path, Networking, and Accelerators.

Integrated Omni-Path options have already been seen in Xeon Phi based products from the Knights Landing family, which occupy the same LGA3647 socket, so it is perhaps not surprising that it looks like Intel will offer some Skylake-SP Xeons with Omni-Path also integrated.

Integrated Networking (asides from OmniPath) would suggest that Intel is looking towards deeper 1000Base-T (gigabit) options and even perhaps a nod to 10G, although this would most likely be provided by additional options on the chipset rather than on the processor (and stems from system integrator leaks we have already seen.

As for integrated accelerators, here Intel mentions Intel QuickAssist (QAT) and AVX-512. AVX-512 is the next advancement in AVX instructions and we already see them in use with Xeon Phi, and we expect there to be the capabilities in silicon to run AVX-512 natively in Skylake-SP. Intel’s QAT is something we’ve seen in standalone PCIe cards before, so it would seem that Intel is also integrating this into the platform. After speaking with users familiar with QAT, due to what is needed to get QAT running at full speed, it would suggest that QAT will be chipset derived and platform dependent rather than purely on the processor.

On the right hand of this slide, Intel mentions FPGA, Nervana, Xeon Phi and Silicon Photonics. The acquisition of Altera for $16.7 billion in 2015 put FPGA integration firmly on the roadmap for Intel’s Xeon product line, however Intel has not officially stated how these will be provided with the new Xeon-SP platforms. The fact that it isn’t listed under the integrated options suggests that Intel will only offer FPGAs as add-in cards (or add-in processors, like Xeon Phi, for dual socket systems) at this time. Intel is also working on new optimized frameworks for the hardware, particularly math and AI libraries.

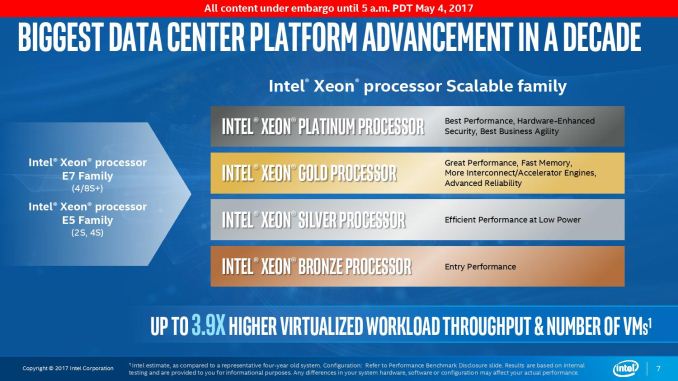

So along with the Gold and Platinum processors we saw last week, Intel will also be introducing Bronze and Silver grades as well. The Bronze group is aimed at entry performance, which sounds like the older low core count E5 parts, while the Silver parts seem aimed at lower power and will probably be low base frequency parts. The Xeon Gold family is aimed at accelerators and interconnects, which suggests they will be for multi-GPU or multi-socket platforms, while the Xeon Platinum will be the cream.

Despite this potential correlation, we were told in our briefing, given by Lisa Spelman, VP and GM of the Data Center Group, that the previous E5/E7 naming split due to potential socket configurations goes away and now we should expect to see various CPUs in all segments correlating to a variety of socket configurations. One of the reasons for this is that sometimes a customer could take advantage of an 8-socket variant processor (due to high cache per core, for example), but would never consider it because the customer only needed a two-socket configuration. One of the reasons given for the naming is to alleviate this issue.

It also means that we might see a lot more product SKUs coming to market, each with different configurations, naming, and capabilities depending on the accelerators. Typically Intel produces three dies for each Xeon generation – a low core count (LCC), a medium/high core count (MCC/HCC), and an extreme core count (XCC) version, and we see a variance up and down the stack depending on what dies fit in where: e.g. LCC were for single socket. With the new Scalable Processor Family naming scheme, we were told that Intel is trying to move away from this differentiation and just provide what the customer needs in the right segment. Not so much integration through obfuscation, but I kindly requested that when the official announcements are made, that the differentiations were made clear. Given the Gold/Platinum processor lists last week, it was unclear exactly what the numbering schemes represented, so in order to make the transition, it needs to be crystal clear.

We were told that as this is the first generation of the Xeon-SP naming scheme, the generation is omitted from the name, but future product lines (Kaby Lake-SP) will have a generational marker to denote the difference. This may be in the form of v2/v3, but this isn't clarified at this time.

Intel isn’t announcing any products today. This is more of an opportunity to take hold of the news that already exists, and perhaps get a step up ahead of the upcoming conference season. We were told to expect a launch in the middle of the year, and were told that Intel is still on track for that.

21 Comments

View All Comments

Draven31 - Tuesday, May 9, 2017 - link

Six-channel memory.... yow!