AMD Zen 2 Microarchitecture Analysis: Ryzen 3000 and EPYC Rome

by Dr. Ian Cutress on June 10, 2019 7:22 PM EST- Posted in

- CPUs

- AMD

- Ryzen

- EPYC

- Infinity Fabric

- PCIe 4.0

- Zen 2

- Rome

- Ryzen 3000

- Ryzen 3rd Gen

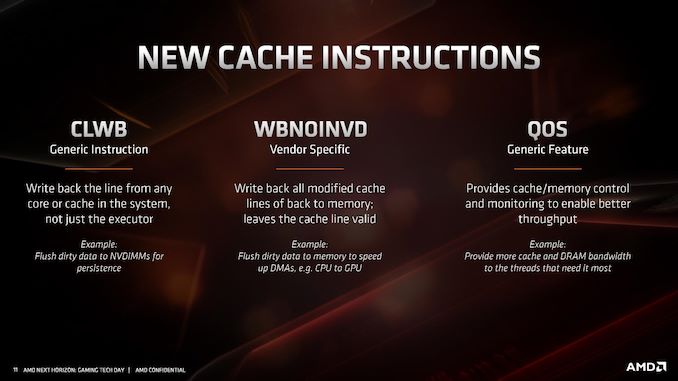

New Instructions

Cache and Memory Bandwidth QoS Control

As with most new x86 microarchitectures, there is a drive to increase performance through new instructions, but also try for parity between different vendors in what instructions are supported. For Zen 2, while AMD is not catering to some of the more exotic instruction sets that Intel might do, it is adding in new instructions in three different areas.

The first one, CLWB, has been seen before from Intel processors in relation to non-volatile memory. This instruction allows the program to push data back into the non-volatile memory, just in case the system receives a halting command and data might be lost. There are other instructions associated with securing data to non-volatile memory systems, although this wasn’t explicitly commented on by AMD. It could be an indication that AMD is looking to better support non-volatile memory hardware and structures in future designs, particularly in its EPYC processors.

The second cache instruction, WBNOINVD, is an AMD-only command, but builds on other similar commands such as WBINVD. This command is designed to predict when particular parts of the cache might be needed in the future, and clears them up ready in order to accelerate future calculations. In the event that the cache line needed isn’t ready, a flush command would be processed in advance of the needed operation, increasing latency – by running a cache line flush in advance while the latency-critical instruction is still coming down the pipe helps accelerate its ultimate execution.

The final set of instructions, filed under QoS, actually relates to how cache and memory priorities are assigned.

When a cloud CPU is split into different containers or VMs for different customers, the level of performance is not always consistent as performance could be limited based on what another VM is doing on the system. This is known as the ‘noisy neighbor’ issue: if someone else is eating all the core-to-memory bandwidth, or L3 cache, it can be very difficult for another VM on the system to have access to what it needs. As a result of that noisy neighbor, the other VM will have a highly variable latency on how it can process its workload. Alternatively, if a mission critical VM is on a system and another VM keeps asking for resources, the mission critical one might end up missing its targets as it doesn’t have all the resources it needs access to.

Dealing with noisy neighbors, beyond ensuring full access to the hardware as a single user, is difficult. Most cloud providers and operations won’t even tell you if you have any neighbors, and in the event of live VM migration, those neighbors might change very frequently, so there is no guarantee of sustained performance at any time. This is where a set of dedicated QoS (Quality of Service) instructions come in.

As with Intel’s implementation, when a series of VMs is allocated onto a system on top of a hypervisor, the hypervisor can control how much memory bandwidth and cache that each VM has access to. If a mission critical 8-core VM requires access to 64 MB of L3 and at least 30 GB/s of memory bandwidth, the hypervisor can control that the priority VM will always have access to that amount, and either eliminate it entirely from the pool for other VMs, or intelligently restrict the requirements as the mission critical VM bursts into full access.

Intel only enables this feature on its Xeon Scalable processors, however AMD will enable it up and down its Zen 2 processor family range, for consumers and enterprise users.

The immediate issue I had with this feature is on the consumer side. Imagine if a video game demands access to all the cache and all the memory bandwidth, while some streaming software would get access to none – it could cause havoc on the system. AMD explained that while technically individual programs can request a certain level of QoS, however it will be up to the OS or the hypervisor to control if those requests are both valid and suitable. They see this feature more as an enterprise feature used when hypervisors are in play, rather than bare metal installations on consumer systems.

216 Comments

View All Comments

fmcjw - Tuesday, June 11, 2019 - link

All good and fine, but I want Zen 2 and 7nm on my laptop. If they aren't announcing it today, products aren't gonna ship by holiday 2019, and most consumers will end up buying 10nm Intel devices. Missed chance.mode_13h - Tuesday, June 11, 2019 - link

Eh, they have perfectly good 12 nm laptop SoCs. 7 nm would've been nice, but it's hard to do everything at once.levizx - Tuesday, June 11, 2019 - link

Nope, those 12nm APUs have worse battery life (than current 8th Gen) and no TB3/USB4 support. I can't think of a reason where I would choose Ryzen 3xxxU over Ice Lakemode_13h - Tuesday, June 11, 2019 - link

Do price & availability count?Xyler94 - Tuesday, June 11, 2019 - link

Misleading remarks. Huawei was able to make a Ryzen APU have better battery life than an 8th gen processor. TB3 and USB4 aren't readily used mainstream yet. Heck USB-C hasn't even caught on yet.Currently laptop makers aren't optimizing AMD's CPU, that's just the fact.

Cooe - Wednesday, June 12, 2019 - link

This is mostly nonsense. Performance AND battery life for Ryzen Mobile 2nd Gen is extremely close to Intel's current 8th & 9th gen 4-core parts. And until Ice Lake is a real thing that you can actually buy, Ryzen still has a major value advantage + far better iGPU performance. Ice Lake also isn't really any faster CPU wise than Whiskey Lake, because despite increasing IPC by +18%, clock-speeds were dropped from 4.8 to 4.1GHz, or about -16%, erasing nearly all those gains.fmcjw - Tuesday, June 11, 2019 - link

Yeah, I get that they still need time to get the GPU down to 7nm, so they pushed it back to focus on the CPU for desktop (where performance per watt matters much less than server or mobile). But the silence is not reassuring, and mobile-wise, Zen is still inferior to Intel, maybe not performance-wise as Huawei demonstrates with its Matebook, but definitely battery-wise because of the more powerful GPU.scineram - Tuesday, June 11, 2019 - link

Nobody is going to buy Shintel vaporware. Or only very few.The_Assimilator - Tuesday, June 11, 2019 - link

Please edit the table on page 1 to combine the rows with identical values into a single row (e.g. the RAM speed). Also edit the 3950X price to have a ? after it as it's not yet confirmed.jfmonty2 - Tuesday, June 11, 2019 - link

The 3950X price is most definitely confirmed; Lisa Su said it loud and clear (and showed it on the slide) in AMD's E3 presentation yesterday: https://www.youtube.com/watch?v=yxPBXNuX6Xs&t=...